## Performance Analysis of Distributed Real-Time Embedded Systems

Master thesis

M.M.C.M. de Hoon (535078)

22nd December 2005

## Performance Analysis of Distributed Real-Time Embedded System M.M.C.M. de Hoon

Final report for Master of science project conducted from December 2004 - December 2005

Department of Electrical Engineering Information and Communication Systems/Electronic Systems  $({\rm ICS/ES})$  Technische Universiteit Eindhoven

#### **Professor:**

Prof.dr.ir. R.H.J.M. Otten (TU/e)

#### Supervisors:

Dr. ir. J.P.M. Voeten (TU/e) M. Sc. O. Florescu (TU/e)

## Abstract

The design of a distributed real-time embedded system is a difficult job. The hardware and software is often designed sequentially, leading to overly conservative and expensive systems. A more reliable and optimal system is obtained by introducing performance analysis in the early design phases. This analysis is performed with models designed in an ad-hoc way.

We propose a method which uses models to analyse distributed real-time embedded systems that capture both functional and timing properties, in a early design phase. The models are based on SHE (Software/Hardware Engineering). SHE is a system-level design methodology based on the formal modelling language POOSL (Parallel Object-Oriented Specification Language), and on the fast execution engine Rotalumis. The modelling method is based on the Y-chart scheme and involves specification of the environment, the application, the architecture and the mapping between them. This thesis presents modelling patterns for common input/output devices, real-time tasks and platform resources. With these patterns a model of a distributed real-time embedded can be build conveniently. The patterns are validated by means of a realistic case study of an in-car navigation system. The outcome of the performance analysis is compared with the outcome of a Modular Performance Analysis (MPA), a method based on worstcase execution analysis. The comparison shows that the proposed method produce performance numbers that approximate the worst case execution as opposed to MPA which is sometimes overly conservative. The proposed method effectively captures the behaviour of both soft and firm real-time embedded systems.

## Acknowledgements

I hereby thank the people from the TU/e ICS/ES department for giving me this opportunity. I would also like to thank Jeroen Voeten, my supervisor, for giving me the opportunity to develop my own ideas. My special thanks goes to Oana Florescu for coaching my during this thesis. From the early stages until the final version she was always able to help me structure my thesis and gave me helpful feedback to improve my work. I also want to thank Marcel Verhoef, a member of the Embedded System Institute, for giving me the In-Car navigation system case study.

Finally, I wish to express my thanks to my family and friends, who have supported me during my time on the TU/e and my graduation. Especially my parents for giving me the chance to continue my study at the University and their support in reaching this goal.

Eindhoven, December 2005 Menno de Hoon

## Contents

| Al | bstra | ct                                                 | i  |

|----|-------|----------------------------------------------------|----|

| A  | cknov | wledgements                                        | i  |

| 1  | Intr  | roduction                                          | 1  |

|    | 1.1   | Problem definition                                 | 1  |

|    | 1.2   | Objectives                                         | 2  |

|    | 1.3   | Main contributions                                 | 2  |

| Li | st of | Figures                                            | 1  |

| 2  | Mo    | delling approach                                   | 5  |

|    | 2.1   | Introduction                                       | 5  |

|    | 2.2   | Software/Hardware Engineering (SHE)                | 6  |

|    | 2.3   | Parallel Object Oriented Specification Language    | 6  |

|    | 2.4   | Tools                                              | 7  |

|    |       | 2.4.1 SHEsim                                       | 7  |

|    |       | 2.4.2 Rotalumis                                    | 7  |

|    | 2.5   | Modelling Method                                   | 7  |

|    | 2.6   | Report Structure                                   | 8  |

| 3  | Mo    | delling of Functional Characteristics              | 11 |

|    | 3.1   | Introduction                                       | 11 |

|    | 3.2   | Environment Modelling                              | 12 |

|    |       | 3.2.1 Registering of Timing Properties             | 12 |

|    |       | 3.2.2 Modelling Sporadic Event Streams             | 14 |

|    |       | 3.2.3 Modelling Periodic Event Streams             | 14 |

|    |       | 3.2.4 Modelling Periodic Event Streams with Jitter | 15 |

|    |       | 3.2.5 Receiving Event Streams                      | 16 |

|    | 3.3   | Application modelling                              | 17 |

|    |       | 3.3.1 Software Tasks                               | 17 |

|    |       | 3.3.2 Communication Tasks                          | 18 |

| 4  | Mo    | delling of Architecture characteristics            | 21 |

|    | 4.1   | Introduction                                       | 21 |

|    | 4.2   | Modelling of Computation                           | 22 |

|    |       | 4.2.1 Static Time Slicing Scheduling               | 23 |

|    |       | 4.2.2 Priority Based Scheduling                    | 24 |

|    |       | 4.2.3 Earliest Deadline First Scheduling           | 25 |

|    | 4.3   | Modelling of Communication Resources               | 26 |

| 5  | Mai   | pping                                              | 29 |

| 6                         | $\mathbf{A} \mathbf{c}$ | ase study: Distributed In-car radio navigation system       | 33 |

|---------------------------|-------------------------|-------------------------------------------------------------|----|

|                           | 6.1                     | Introduction                                                | 33 |

|                           | 6.2                     | Distributed In-Car Radio Navigation System                  | 33 |

|                           | 6.3                     | POOSL Model                                                 | 36 |

|                           |                         | 6.3.1 Worst Case Performance Analysis                       | 37 |

|                           | 6.4                     | Modular Performance Analyse                                 | 39 |

|                           | 6.5                     | POOSL and MPA Comparison                                    | 42 |

|                           | 6.6                     | Average Performance Analysis                                | 43 |

|                           |                         | 6.6.1 Reduction of Resource Performance                     | 46 |

|                           |                         | 6.6.2 Approximation of Worst Case Performance               | 48 |

| 7                         | Con                     | aclusion and recommendations                                | 49 |

|                           | 7.1                     | Realised Objectives and conclusion                          | 49 |

|                           | 7.2                     |                                                             | 50 |

| A                         | Sim                     | ulation Results of the Distributed In-car Navigation System | 51 |

|                           | A.1                     | Performance results of architecture A                       | 51 |

|                           | A.2                     | Performance results of architecture B                       | 51 |

|                           |                         | Performance results of architecture C                       | 52 |

|                           | A.4                     | Performance results of architecture D                       | 52 |

|                           |                         | Performance results of architecture E                       | 52 |

| A                         | Rea                     | l-time calculus definitions                                 | 53 |

|                           | A.1                     | Min-plus Convolution and Deconvolution                      | 53 |

|                           |                         | Max-plus Convolution and Deconvolution                      | 53 |

| $\mathbf{R}_{\mathbf{c}}$ | efere                   | nces                                                        | 55 |

# List of Figures

| 2.1  | Two execution phases of a POOSL model                                | 7  |

|------|----------------------------------------------------------------------|----|

| 2.2  | The Y-chart design approach                                          | 8  |

| 2.3  | Structure of the report based on the Y-chart                         | 9  |

| 3.1  | Simple view of a real-time embedded system in an environment         | 11 |

| 3.2  | Timing properties of events                                          | 12 |

| 3.3  | POOSL specification of the EventProperties data class                | 13 |

| 3.4  | Sporadic event stream generated by an event component                | 14 |

| 3.5  | POOSL specification of a sporadic event stream                       | 14 |

| 3.6  | Periodic event stream generated by an event component                | 15 |

| 3.7  | POOSL specification of a periodic event stream                       | 15 |

| 3.8  | Periodic event stream with jitter generated by an event component.   | 15 |

| 3.9  | POOSL specification of the jitter generator class                    | 16 |

| 3.10 | POOSL specification of a periodic event stream with jitter           | 16 |

|      | POOSL specification of a receiving event model                       | 16 |

|      | Application model represented as a directed task graph               | 18 |

|      | POOSL specification of a periodic event stream                       | 18 |

| 3.14 | Application model consist of application and communication com-      |    |

|      | ponents                                                              | 19 |

| 3.15 | Communication interpretation of a distributed real-time embedded     |    |

|      | system. The communication is specified as a communication task       |    |

|      | executed on a resource model. The incoming event represent the       |    |

|      | head of the message and the outgoing event represents the tail of    |    |

|      | the message                                                          | 19 |

| 3.16 | POOSL specification of a functional communication component          | 20 |

| 4.1  | Architecture modelled as decoupled SHE components                    | 21 |

| 4.2  | An example of a specification of an architecture which consist of    |    |

|      | three processor cores and one shared bus                             | 22 |

| 4.3  | An example of a specification of an architecture which consist of    |    |

|      | two processor cores and one shared bus                               | 22 |

| 4.4  | POOSL specification of a computation component without scheduler     | 23 |

| 4.5  | Task queue of a time line scheduling algorithm                       | 23 |

| 4.6  | POOSL specification of a preemptive computation resource based       |    |

|      | on the static time slicing scheduler                                 | 24 |

| 4.7  | POOSL specification of computation with priority scheduling policy   | 25 |

| 4.8  | This POOSL specification is needed in figure 4.7 to model a earliest |    |

|      | deadline first scheduler                                             | 26 |

| 4.9  | General communication networks                                       | 26 |

| 4.10 | POOSL specification of a direct point-to-point communication re-     |    |

|      | source                                                               | 26 |

| 5.1  | Mapping phase                                                        | 29 |

| 5.2  | Mapping of application and architecture models where the commu-           |    |

|------|---------------------------------------------------------------------------|----|

|      | nication channels defines the hardware structure of the system            | 30 |

| 5.3  | Sequence diagram of communication for execution demand in the             |    |

|      | mapping phase                                                             | 30 |

| 6.1  | High-level of a distributed radio navigation system                       | 34 |

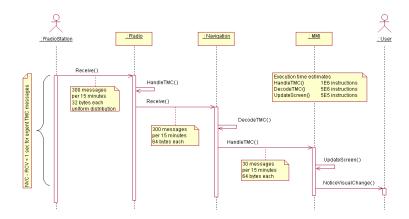

| 6.2  | Annotated Sequence Diagram for "Change Volume"                            | 34 |

| 6.3  | Annotated Sequence Diagram for "Address Look-up"                          | 35 |

| 6.4  | Annotated Sequence Diagram for "TMC Message Handling"                     | 36 |

| 6.5  | Alternative system architecture to explore                                | 36 |

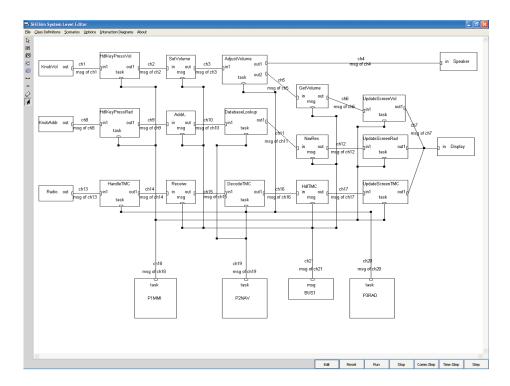

| 6.6  | SHEsim model of architecture A                                            | 37 |

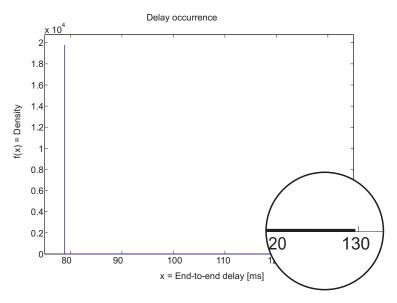

| 6.7  | Occurrence of ADDR delays when ADDR and TMC are executed                  |    |

|      | in parallel on architecture A                                             | 38 |

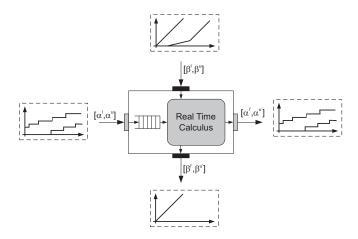

| 6.8  | A basic performance component with abstract models as input and           |    |

|      | output and Real-Time Calculus to process internal transformations.        | 39 |

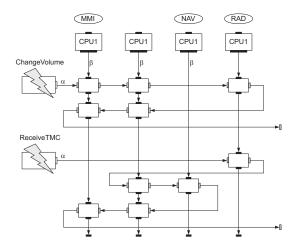

| 6.9  | MPA model for system architecture A of figure 6.5                         | 40 |

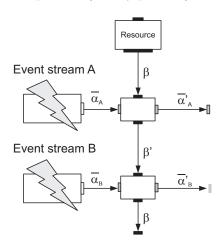

| 6.10 | MPA model of two event streams sharing one resource                       | 40 |

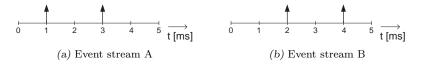

| 6.11 | Event stream A and B in milliseconds                                      | 40 |

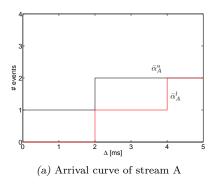

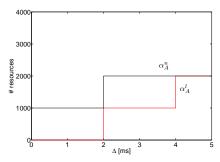

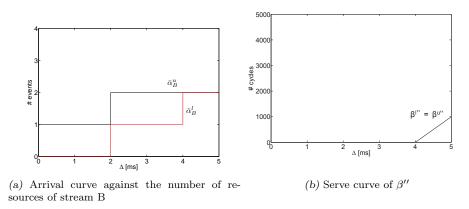

| 6.12 | Arrival curves of Stream A, (a) number of events against $\Delta$ , (b)   |    |

|      | number of resource against $\Delta$                                       | 41 |

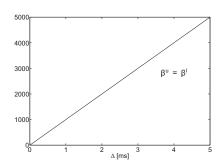

| 6.13 | (a) Resource curves of $\beta$ and $\beta'$                               | 41 |

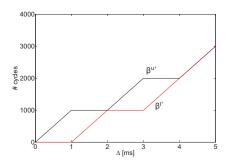

| 6.14 | Arrival and serve curve of event stream B                                 | 42 |

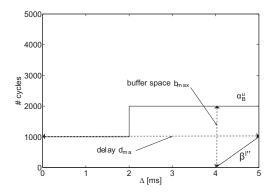

| 6.15 | Maximum delay and maximum buffer space obtained from arrival              |    |

|      | and service curves                                                        | 42 |

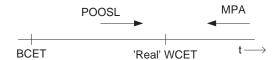

| 6.16 | Timing diagram which visualise the domain of POOSL and MPA                |    |

|      | analysis                                                                  | 43 |

|      | Delay frequency functions of scenario VOL, ADDR and TMC $\cdot$ . $\cdot$ | 45 |

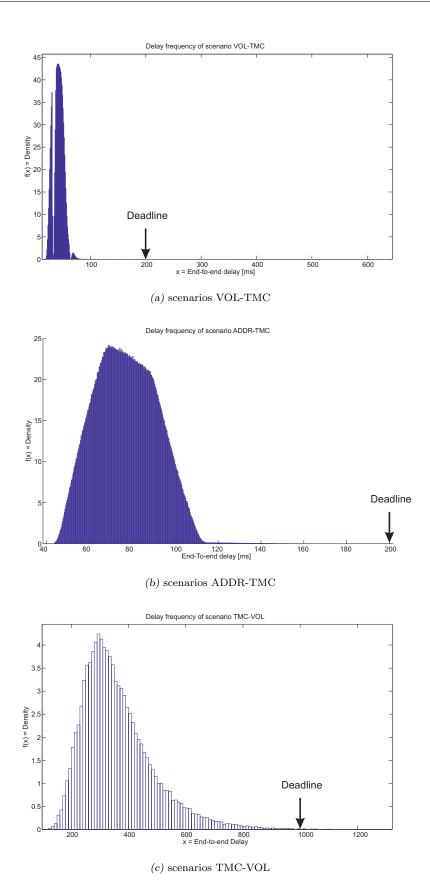

| 6.18 | Frequency delay functions of scenarios VOL-TMC, ADDR-TMC                  |    |

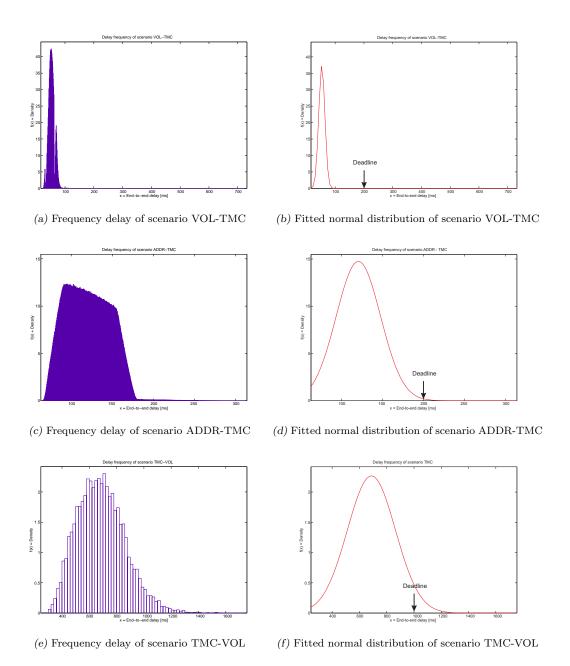

|      | and TMC-VOL when instruction load has a uniform distribution .            | 47 |

## Chapter 1

## Introduction

The real-time embedded systems industry today must realise its product ideas even quicker than in the past. To be competitive, these new real-time embedded systems must support more functionality, make use of latest technical innovations and, of course, must be low cost. Real-time embedded systems which support much functionality are complex and hard to design. The industry often uses methods to specify hardware and software separately, often leading to overly conservative systems. Overly conservative systems largely contribute to the product cost. One of the reasons is the lack of a proper modelling methodology to give insight in the behaviour of the system, which would help in finding the optimal hardware and software combination. A modelling methodology enables modelling of complex real-time embedded systems and provides insight in the behaviour of the system in the early design phases. Such modelling methodologies must take both the software and the hardware part of embedded system into account. This eventually must result in a reliable and optimal embedded system, designed in less time.

## 1.1 Problem definition

Existing design methods, for instance object-oriented design methods, focus on reusing and maintaining large systems. These design methods have proven their benefit especially for traditional software development. However these methods are not adequate for designing real-time embedded systems. A design method for real-time embedded system should provide a modelling technique that can appropriately capture functional and timing properties. A design method called Software/Hardware Engineering (SHE) is presented in [1]. SHE is a system-level design methodology based on the formal modelling language POOSL (Parallel Object-Oriented Specification Language), and on the fast execution engine Rotalumis. The POOSL models can be specified with the graphical tool SHESim. The methodology allows specification and analysis of real-time discrete-event control systems, such as a high-speed packet-switch, a network processor, a printer controller and a wafer-stepper controller. The specification of these system is done ad-hoc. A suitable way to model and analyse these kinds of systems is necessary. Therefore a modelling method should provide an approach to model a system in an adequate way. To speed up the design process a method should be supported by a library. This library must contain components that have common characteristics of a real-time embedded system. To simplify the design space explorations these patterns must be modular (plug-and-play).

## 1.2 Objectives

The objectives in this thesis to cope with problem definition are given in the following enumeration:

- 1. Develop a modelling method which is suitable for performance analysis and design space exploration of distributed real-time embedded systems. A modelling method should be defined which helps to design a model of a real-time embedded system. The model needs to capture both the functional and timing behaviour and should be suitable for performance analysis. This method should be supported with a library which consists of a basic set of components that capture common characteristics of a real-time embedded system. The use of predefined components must speed up the modelling process. A modular design approach should simplify the design space exploration.

- 2. Show applicability of the modelling method. The applicability of the method should be demonstrated by an industrial case study. A performance analysis should be used to validate the components of the modelling method.

## 1.3 Main contributions

During the project we developed a method for modelling distributed real-time embedded systems. This modelling method describes how to capture both functional and timing behaviour. The method is based on the Y-chart. The Y-chart scheme structure a system for design space exploration. For each part of the Y-chart scheme we present components which models common characteristics of real-time embedded systems. The following list presents parts of the Y-chart scheme.

- Environment: In the environment section components characterise common input and output devices of a real-time embedded system by generating event patterns.

- **Application:** The application section defines the functional behaviour of a real-time embedded system.

- Architecture: Architecture components characterises processor and communication resources. The processor components models the computation with rate monotonic, earliest deadline first or time sliced scheduling. The communication components model data exchange with a first come first serve discipline.

- Mapping: In the mapping section we have specifies how an application is mapped on an architecture in a modular way.

- **Performance analysis:** By analysing the combined model the performance properties (throughput, occupation, delay, etc.) can be deduced.

All these components are specified in a modular way (plug-and-play) which simplifies the exploration of the design space. The method was validated by means of a realistic industrial case study. The outcome of the performance analysis is compared with the outcome of a Modular Performance Analysis (MPA), a method based on worst-case execution analysis. The comparison showed that POOSL performance numbers approximate the worst case execution and MPA is sometimes overly conservative. As the POOSL analysis technique relies on simulation; the discovery of the worst case execution can not be claimed. Moreover,

the accuracy of the performance results depends on the simulation length. However the advantage is that the realistic behaviour of the system can be captured using distributions.

## Chapter 2

## Modelling approach

## 2.1 Introduction

Real-time embedded systems are difficult to design. They consist of both hardware and software components. The technological advance and the demand for more functionality make these systems more complex. The software behaviour in a real-time embedded system depends on the system hardware (architecture). Typically, software and hardware design methodologies are applied in isolation, which, after the combination of their results, result in an over-dimensioned or even non-working system. Some of the classical design methodologies are:

- Structured analysis and design methods (Ward and Mellor [2], Hatley and Pribhai [3])

- Object-oriented and object-based analysis and design methods (UML [4], ROOM [5], etc.)

- Formal description methods (SDL [6], Estelle [7])

For a complete comparison of these methodologies see [1] and [8]. These classical design methodologies do not often adequate help the design process in considerate design alternatives for realising the desired functionality. Early in the design process, the choice for a specific design alternative may have a deep impact on, for example, the performance of the final implementation. To assist the designer in taking well-founded design decisions, system-level design methodologies can be applied. A system-level methodology which supports the construct models that allows the analysis of the system in the early design phase is very helpful.

A suitable modelling methodology which can be used for modelling real-time embedded systems is the Software/Hardware Engineering (SHE) introduced in [1] and briefly described in section 2.2. This modelling methodology has proven its usefulness in modelling several kinds of real-time embedded systems, like [9], [10] and [11]. The designer experienced several disadvantages during the modelling process, such as; a long modelling time, the low degree of reusability and that each model is complex. A reason for this is that these models are modelled without applying a method. The advantages of applying a method for modelling a real-time embedded system are:

• Reducing the modelling time. The construction of a real-time embedded system is done by the use of components. The modelling time can be reduced when the designer is able to re-use earlier designed components. To overcome inconsistency these components must comply with the (interface) specifications described in the upcoming chapters.

- Understandability. A predefined subdivision of how to model a real-time embedded system model will increase readability.

- Analysability. A method is taking care of the possibility to perform a system analyse, for example the performance or occupation.

- Assist the designer in taking well-founded design decisions. Applying a method that uses components and predefined system subdivision allows a Design Space Exploration (DSE). A DSE helps the designer to take well-founded design decisions.

In this thesis a modelling method is described to improve the modelling process. The method is extended with several examples of components which can be used for modelling (distributed) real-time embedded systems. These components are specified in the expressive modelling language POOSL, formalised in [1]. A short description of POOSL is given in section 2.3. The tools used for specification and execution of the POOSL components, namely SHEsim and Rotalumis, are briefly discussed in section 2.4. In section 2.5 and 2.6 the guidelines of the modelling method, which is the content of this thesis.

## 2.2 Software/Hardware Engineering (SHE)

SHE is a system-level design methodology, as defined in [12], that allows analysis of both correctness and performance properties of design alternatives based on models. To construct such models, SHE uses Parallel Object-Oriented Specification Language (POOSL) to formulate and formalise the behaviour of a system. The actual evaluation is based on the application of several techniques for formal verification of correctness properties and performance analysis. A key feature of the SHE methodology is that it is based on formal methods which ensures that the obtained analysis results are unambiguous.

# 2.3 Parallel Object Oriented Specification Language

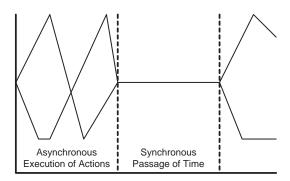

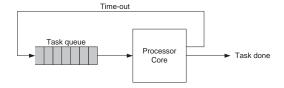

In this section, we present a brief overview of the POOSL (Parallel Object Oriented Specification Language) language, which was developed at Eindhoven University of Technology. POOSL is a very expressive modelling language with a small set of powerful primitives whose semantics are defined with mathematical axioms and rules. POOSL can describe concurrency, distribution, communication, timing and functional features of a system in a single executable model. POOSL consists of a process part and a data part. The process part (processes and clusters) is based on a real-time extension of the process algebra CCS [13]. This part is specified in components which performs certain functionality of a system. The data part are passive components that specify the information that is generated, exchanged, interpreted or modified by the system. The data part is based upon the concepts of traditional sequential object-oriented programming languages like Smalltalk and C++. The execution of a POOSL model is based on a two phases execution model [14], as shown in figure 2.1. The state of a model can either change by asynchronously executing atomic (communication or data processing) actions (taking no time) or by letting the time pass (synchronously).

The formal semantics of POOSL enable the application of model checking techniques for formal verification of correctness properties and Markov-chain based performance analysis techniques. Furthermore, it serves as basis for a timing property-preserving approach for real-time software synthesis.

Figure 2.1: Two execution phases of a POOSL model.

## 2.4 Tools

#### 2.4.1 SHEsim

SHESim is an interactive modelling and simulation tool, which enables the construction of complex concurrent systems in accordance with the SHE methodology. It is used to incrementally specify and modify POOSL data classes, process classes and cluster classes. SHESim allows the (graphical) entry of POOSL models and their interactive simulation. The messages and parameters that are passed between the different processes and clusters are indicated on the appropriate channels. To inspect the history of messages that have been exchanged between different entities, interaction diagrams can be generated automatically during a simulation. For more information see [15].

#### 2.4.2 Rotalumis

Rotalumis is a high-speed execution engine which allows fast simulations of POOSL models. In comparison with the execution speed of the SHEsim tool where the execution takes place in an interpretive way, the execution speed is improved by a factor of 100. Rotalumis compiles the POOSL model into intermediate format that is executed on a virtual machine implemented in C++. For more information see [16]. This academic tool was used for the simulation of all models presented in this thesis. In general, the models are validated in the SHEsim tool and then executed in Rotalumis.

## 2.5 Modelling Method

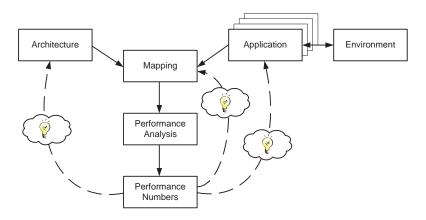

The guideline of the modelling method is based on the Y-chart scheme structure. As described in [17], the Y-chart with one extension involves the following:

- Environment: Specify the environment behaviour capturing the characteristics of the surroundings, such as input and output devices connected to the real-time embedded system.

- **Application:** An abstraction of the software is defined in the application section. The environment is linked to a set of tasks in the application section. The environment triggers this set of tasks.

- Architecture: The modeler describes a particular architecture of the realtime embedded system.

- Mapping: In this section the application is mapped on the architecture.

- **Performance analysis:** The mapped architecture and application model are used for performance analysis.

- **Performance numbers:** This analysis yields performance numbers which can propose improvements in the architecture, application and/or mapping. This processes is indicted in figure 2.2 by the light bulbs.

Figure 2.2: The Y-chart design approach.

This procedure can be repeated in an iterative way until a satisfactory architecture, set of application and mapping is found. To be able to use the Y-chart approach, the following modelling steps must be followed:

- 1. Specify the environment components.

- 2. Specify the application.

- 3. Specify the architecture components.

- 4. Map application components onto the architectural components.

- 5. Analyse the performance.

The specification of the functional part of the real-time embedded system is described in steps 1 and 2, where the specification of the environment and application models are made. The functional part is "independent" of the architecture specified in step 3. Step 4 is to map the application to the architectural components. After applying the performance analysis, steps 2 till 4 can be reconsidered for optimisation of the system. This modelling process gives the engineer a structured framework to explore the design space of a computation intensive real-time embedded system.

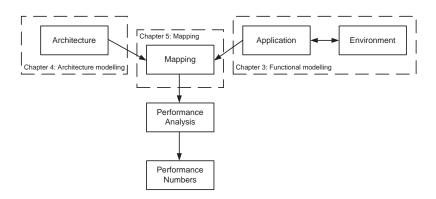

## 2.6 Report Structure

The structure of this report follows the earlier presented Y-chart scheme, see figure 2.3. The functional model which specifies the environment and application components, is described in chapter 3. The application components require architectural components for execution. The architectural modelling is described in chapter 4. The mapping of the application components onto the architectural components is discussed in chapter 5. Chapter 6 shows the utilisation of the described design approach in a case study. Chapter 7 provides the conclusions and future work related to this thesis.

$Figure\ 2.3:$  Structure of the report based on the Y-chart.

## Chapter 3

# Modelling of Functional Characteristics

## 3.1 Introduction

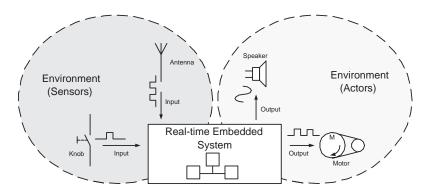

A real-time embedded system performs software tasks that are executed on processors. These software tasks are activated by the working environment of the system. The software tasks and the working environment belong to the functional part of a real-time embedded system model. Figure 3.1 visualises an example of a real-time embedded system in a working environment which helps engineers reason about the total system behaviour. **Note:** These graphical representations are

Figure 3.1: Simple view of a real-time embedded system in an environment.

not restricted by drawing rules; their purpose is to clarify the system and working environment.

To model the functional characteristics of a real-time embedded system, the design consists of environment and application components. The environment components model the characteristics of the environment given by input and output devices. Some examples of such devices are sensors, knobs, antennas, motors, speakers and displays. The application components model the software part of a real-time embedded system which are presented as a directed graph of tasks. Event activation patterns generated by the environment components are used for modelling the behaviour of input devices connected to the real-time embedded system.

This chapter is organised as follows:

- Subsection 3.2 describes an approach to model the environment of a realtime embedded system, by use of several kinds of event patterns.

- Subsection 3.3 presents a pattern to model an application, which reflects the software part of the system.

## 3.2 Environment Modelling

The functional characteristics of the environment are specified in environment components. Environment component models the generation or consumption of event streams. In an event stream each event has a specific time at which it must occur. These event streams are specified as having periodic or sporadic patterns. [18] and [19] define a set of such general event patterns. Important patterns for analysing performance of a real-time embedded systems are events that occur sporadically, periodically (with jitter) or within a burst. Our modelling approach uses a data object to exchange event-related information such as timing variables. This event-related information can be updated during simulation. The specification of this data class is described in section 3.2.1. Sections 3.2.2, 3.2.3 and 3.2.4 describe possible event patterns which commonly occur in real-time embedded system and are suitable for modelling. Finally, section 3.2.5 describes a modelling component which consumes the event stream passed through the system model.

## 3.2.1 Registering of Timing Properties

The complete model is used to predict the performance of a real-time embedded system. A data class which registers performance properties is used in this modelling method. A new data object is initialised each time when an environment component generates an event. At this moment the release time of the event is registered in this data object. When the environment component triggers the application model (described later on) by an event the start time is registered in the data object. During the execution of the application model the data object is exchanged between tasks. Each task updates the communication or computation variable when it is involved with in, respectively, communication or computation. Finally, the data object will reach a consuming environment component which register the finish time.

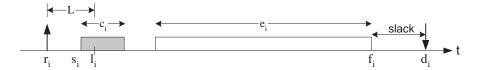

POOSL allows the creation of data objects, which are instances of data classes, for modelling passive components (see [20] for more details). Each time when an environment component generates an event, it exchanges this data by sending the data object (making a Deepcopy) along with a message to another component. A characterisation of the timing properties is given in figure 3.2. In this illustration,

Figure 3.2: Timing properties of events.

i stands for the identification number of the event. A description of the illustrated properties are given below:

Release time  $r_i$ : is the time at which an event becomes ready for execution;

**Start time**  $s_i$ : is the time at which a task start its execution;

End of release  $l_i$ :  $l_i = r_i + L$  is the time when the event is not able to trigger a task anymore;

**Event Lifetime** L: is the amount of time an event is active and able to trigger a task:

**Finish time**  $f_i$ : is the time at which an event finishes its execution;

Communication time  $c_i$ : is the time used by the communication link;

Computation time  $e_i$ : is the time necessary to the processor for executing the task;

**Deadline**  $d_i$ : is the moment before which a task should be completed to avoid damage to the system;

**Slack**:  $X_i$ :  $X_i = d_i - f_i$  is the maximum time an event can be delayed on its release to complete within its deadline;

Note that such a data object is exchanged by several tasks in the application model. Every time the data object is in a new task component, the current values of the communication and computation time are accumulated with the new communication or computation time.

The timing properties are defined in the EventProperties data class which modifies and registers the above presented timing properties. Figure 3.3 presents the EventProperties data class specified in POOSL. Methods SetReleaseTime,

```

<< data class >>

EventProperties : Object

<< instance variables >>

Integer

RelativeDeadline: Real

ReleaseTime : Real

StartTime : Real

FinishTime : Real

ComputationTime : Real

CommunicationTime :

<< methods >>

Ini(t : Real) : Object

SetReleaseTime(t : Real) : Object

SetStartTime(t : Real) : Object

SetFinishTime(t : Real) : Object

AddComputationTime(t : Real) : Object

AddCommunicationTime(t : Real)

Object

```

```

1 Ini(t : Real) :

Object

RelativeDeadline := t:

return self.

4 SetReleaseTime(t :

Real) :

5 ReleaseTime := t;

7 SetStartTime(t : Real) : Object

StartTime := t;

8

return self.

10 SetFinishTime(t :

Real) :

Object

11 FinishTime := t;

return self.

13 AddComputationTime

14

(t : Real) :

Object

15

ComputionTime :=

16

ComputionTime + t;

17

return self.

18 AddCommunicationTime

19

(t : Real) : Object

20

CommunicationTime :=

21

CommunicationTime + t:

```

$Figure~3.3:~{\rm POOSL~specification~of~the~EventProperties~data~class}$

SetStartTime and SetFinishTime specify the release, start and finish time respectively of an event captured in an EventProperties data object. When the event data object travels through the application model and reaches a consuming environment component, the timing properties are used for analysis purpose. Methods AddComputationTime and AddCommunicationTime add repetitively computation and communication time in the data object. The following sections describe several components which generate event patterns that use the EventProperties data class.

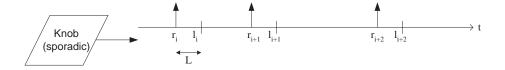

#### 3.2.2 Modelling Sporadic Event Streams

Sporadic event stream components model the activation of an input device connected to the real-time embedded system. This component is used for modelling devices that are activated irregularly, such as a knob or a remote control. An example of a sporadic event stream is given in figure 3.4. At every r in figure 3.4 an

Figure 3.4: Sporadic event stream generated by an event component.

event is released; l denotes the end time of the event lifetime. A task can be triggered by the event between the r and l. The triggering of tasks is only done when the application (the tasks) is capable to serve a new event (the system could be busy). In this way, event misses can be analysed and event releases do not overlap. The specification of a component which produces is given in figure 3.5. In fig-

```

1 ini()()

<< process >>

t := new(Distribution);

SporadicEventModel

3

SporadicEventStream()().

<< instantiation parameters >>

4 SporadicEventStream()()

eventLifetime : real;

5 | E : EventProperties |

<< instance variables >>

E := new(EventProperties)

6

RandomGenerator;

7

SetReleaseTime(currentTime);

<< methods

8

Tni()()

9

abort out!event(E) with

SporadicEventStream()()

10

delay eventLifetime

<< initial method call >>

11

Ini()()

delav (t random + eventLiftime):

12

<< messages >>

13

SporadicEventStream()()

out!event

14

rap

```

Figure 3.5: POOSL specification of a sporadic event stream

ure 3.5 eventLifetime is an instantiation parameter of the SporadicEventModel which specifies the life of an event. The instance t is of a distribution type, and used for generating different time between event actuation. In this example a random distribution is used. To guarantee that the occurrences of events do not overlap other events, the specified eventLifetime is added to the period of the next released event at line 12.

#### 3.2.3 Modelling Periodic Event Streams

Devices connected to an embedded system that have periodic characteristics, like radio antennas and sensors, are modelled as components that generate events periodically. An example of a periodic event pattern is given in figure 3.6, where r, l and T denote respectively the release time, the end of the event actuation lifetime and the period of the event release. A component which generates a periodic event pattern can be specified in POOSL as described in figure 3.7. As the specification in figure 3.6 describes, eventLifetime and period are instance parameters that characterise the event activation pattern. To guarantee that every event is activated at the specified time instances, the PeriodEventStream is specified as a parallel method. In line 5, an event is offered during the specified

Figure 3.6: Periodic event stream generated by an event component.

```

\overline{<<} process >>

PeriodicEventModel

1 PeriodicEventStream()()

<< instantiation parameters >>

| E : EventProperties |

eventLifetime : Real;

E := new(EventProperties) SetReleaseTime(currentTime);

period : Real;

par

instance variables >>

5

abort out!event(E) with delay eventLifetime

<< methods >>

6

and

PeriodicEventStream()()

delay period;

<< initial method call

8

PeriodicEventStream()()

PeriodicEventStream()()

9

<< messages >>

out!event

```

Figure 3.7: POOSL specification of a periodic event stream

eventLifetime. When the amount of time specified in eventLifetime is elapsed the offering of the event is stopped (an event miss).

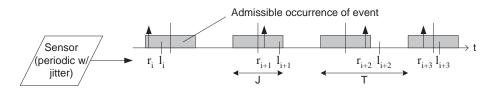

## 3.2.4 Modelling Periodic Event Streams with Jitter

In common distributed real-time embedded systems, input devices produce a fixed number of events in a certain time unit. The exact period between these events is often hard to specify. A component which produces events each period with a jitter is therefore useful. This component is also useful for performance analysis of distributed real-time embedded system where several input devices produce events in different periods. Modelling these input devices with components which generate events periodically will not cover all the states of the system, because combining of periodical events patterns will result in a repetitive occurrence of events. A periodic event pattern with jitter is represented in figure 3.8. In figure

Figure 3.8: Periodic event stream with jitter generated by an event component.

$3.10\,T,\,J,\,r$  and l denote the period, jitter, release time and end of the release time of an event. The event actuation is between  $iT-\frac{1}{2}J$  and  $iT+\frac{1}{2}J$ . To guarantee no event overlap, the abstract environment model must comply with  $T>\frac{1}{2}J+d$ . The environment component which generates jittery events uses the specially defined JitterGenerator data class, which is specified in figure 3.9. The next method in JitterGenerator data class returns a value between  $-\frac{1}{2}J$  and  $+\frac{1}{2}J$ , which eases the specification in an environment component. This JitterGenerator data class is specified with the use of a distribution (see the instance variables). In this example a random distribution (RandomGenerator) is used. An environment component that generates the periodic event stream with jitter is specified in

```

1 SetJitter(i : Real) : Object

2    jitter := i;

3    return self.

4 next() : Real | n : Real |

5    if jitter > 0 then

6    n := (r random * jitter) - (0.5 * jitter)

7    else

8    n := 0;

9    fi;

10    return n.

```

Figure 3.9: POOSL specification of the jitter generator class

POOSL and shown in figure 3.10. As figure 3.8 shows, the jitter is centralised at

```

1 ini()()

jitter := new(JitterGenerator)

3

SetJitter(j);

PeriodicJitterEventStream()().

5 PeriodicJitterEventStream()()

6 | E : EventProperties |

7

par

delay period + jitter next;

9

abort out!event(E) with delay duration

10

delay (period);

11

PeriodicJitterEventStream()()

12

13

rap.

```

Figure 3.10: POOSL specification of a periodic event stream with jitter

each period. This means that the first event can occur at negative time. An event which occur in negative time can not be modelled. The limitation of this process is that the release time of the first event is equal to or bigger than  $T - \frac{1}{2}J$ .

#### 3.2.5 Receiving Event Streams

Each event stream that passes through the application model will be received by the environment model. This environment model reflects the actuator devices connected to a real-time embedded system, like motors, displays, speakers, etc. A simple event consuming component is specified in figure 3.11. This tail-recursive

```

<< process >>

EventReceiverModel

<< instantiation parameters >>

1 ReceiveEvent()()

<< instance variables >>

<< methods >>

2 | E : EventProperties |

ReceiveEvent()()

3

in?event(E);

<< initial method call >>

4

ReceiveEvent()();

ReceiveEvent()()

<< messages >>

in?event

```

Figure 3.11: POOSL specification of a receiving event model

specification of an event consumer component receives event streams from the application model without any restriction. The received event data object E is used especially for analysis purposes.

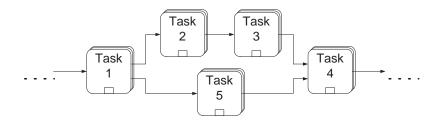

## 3.3 Application modelling

In the Y-chart scheme, presented in figure 2.2, the environment components trigger the application model. The software behaviour of a real-time embedded system is specified in the application model. The application model consists of nodes which represent tasks of the software. During the modelling phase the actual behaviour of a task does not need to be specified. Finding a good abstraction of a task is hard and typically done by experienced engineers. Characteristics and methods to determine proper abstractions of software task is outside the scope of this thesis. The application model is a directed graph where nodes represent tasks and edges represent activation channels. Note that the edges are not necessary infinite FIFO queues as in the case of Kahn Process Networks, introduced in [21]. A task in this model can also block other tasks. Real-time embedded systems consist not only of processors but also of communication resources. The communication taking place in these resources can be seen as tasks, therefore the application model also exists of components which models the communication in the system. Task components used for modelling the software is described in section 3.3.1. In section 3.3.2 the communication tasks are described.

#### 3.3.1 Software Tasks

In the early design phases, where this modelling approach is used, the software of the embedded system is typically not known in detail. To speedup the modelling process, task components model the main functionality of the software. Representing the application model as a directed graph makes it possible to execute tasks in parallel. When a task is triggered by an event it performs an abstracted software task. These active tasks will trigger new task components to model the complete software. Parameters that involve computation behaviour are defined in the task component, however some general parameters are:

Computation load: each task is specified with a computation load, which can be specified in the amount of cycles or instructions (depending on the type of processor architecture used in the system). When specifying an instruction name it is possible to retrieve the computation load out of a predefined computation table specified in the resource component (described in chapter 4);

**Task identifier:** a unique identifier in the application graph, which can be a name or a number. The identifier is used to follow the order in which computations are carried out;

**Priority / relative deadline** [optional]: this number is used for scheduling the computations of tasks;

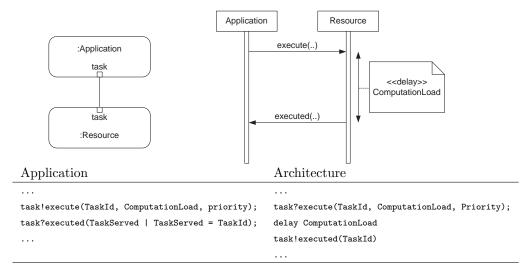

Note that these parameters depend on the resources of the system. Specifying these parameters at the resource components (see chapter 4) will make the model less suitable for exploration of design alternatives (each task must be known by the resource). Figure 3.12 represents a directed task graph which is part of the application model. Note: For reasons of simplification, the communication components are not displayed in this graph. A POOSL specification example of a task component is given in figure 3.13. The described HandleEvent method (line 1 to 9) is tail recursive which allows the task component to serve any incoming event. Each incoming event is served by the Execute method, which sends (as a message) an execution request to the architecture components. The parameters involved in the computation behaviour are also passed through in the message. When the request of a task execution is granted and served at the architecture level (as

Figure 3.12: Application model represented as a directed task graph

```

<< process >>

HandleEvent()()

1

<< instantiation parameters >>

TaskName : String;

2

| E : Event|

3

in?event(E);

ComputationLoad:

4

Priority: Integer;

par

<< instance variables >>

5

6

and

TaskId: Integer;

7

Execute()():

<< methods >>

8

out!event(E)

HandleEvent()()

9

rap.

Execute()()

<< initial method call >>

10 Execute()()

HandleEvent()()

11

Priority);

<< messages >>

12

in!event

13

out?event

14

task!execute

task?executed

```

```

1 HandleEvent()()

2 | E : Event|

3   in?event(E);

4   par

5   HandleEvent()()

6   and

7   Execute()();

8   out!event(E)

9   rap.

10 Execute()()

11   task!execute(TaskId, ComputationLoad,

12   Priority);

13   task?executed(TaskServed)

14   | TaskServed = TaskId).

```

Figure 3.13: POOSL specification of a periodic event stream

described in chapter 4), the task component is returned a message executed and will generate a new event for a new task component. At line 13 and 14 the task receives an acknowledgement (task?executed) when the computation is executed in the architectural level. TaskServed is an identifier which is used to check if the right task is executed.

This specification specifies a task component with one input and one output. Task components with for example multiple inputs and/or output can be specified in the same way. Specifying these kinds of tasks must comply with the message protocol used in this method, which are: the in?event and out!event channels sends and receives an Event data classes; communication with the architecture level is done with the parameters TaskID, ComputationLoad, Priority and TaskServed over the task!execute and task?executed channel.

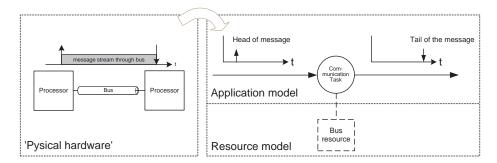

#### 3.3.2 Communication Tasks

As early described, distributed real-time embedded systems commonly consist of communication links. The communication itself depends on the used link (for example bandwidth) and involves the behaviour of the application. In this method the communication taken place over these links are therefore specified in the tasks and resource components. The advantage of this approach is that it improves the exploration of the design space (explore alternative architectures). In this way communication load can easily be mapped on resource component. Each task in the application model exchanges data through communication components, as shown in figure 3.14. From the application point of view, the communication tasks are not specific about the operation of the hardware, with respect to blocking, non-blocking or bandwidth limitation. These communication tasks hold the

Figure 3.14: Application model consist of application and communication components

communication parameters which involve the application behaviour. Some communication parameters which are specified in the communication tasks are:

Message ID: a unique value used for identification;

**Message size** : specified in the amount of bytes needed to transfer; other unities are also allowed.

The incoming event in the communication task represents the tail of the message. The outgoing event of the communication task represents the tail of the transferred message through the link, see figure 3.15. The advantage of this

Figure 3.15: Communication interpretation of a distributed real-time embedded system. The communication is specified as a communication task executed on a resource model. The incoming event represent the head of the message and the outgoing event represents the tail of the message.

approach is that processor resource components are not involved with the communication, which simplifies the modelling process. A disadvantage is that this approach models complete buffering of data, which is not always wanted, for example with multimedia streams. A solution would be to transfer long data stream in segments. On the other hand, specifying a communication bridge takes less effort (an extra software and communication task are needed to be specified). A POOSL specification of a communication task component is given in figure 3.16. The method HandleEvent is initially called when the model is executed. This recursive method receives all incoming events (seen as the tail of the message) and will model information exchange on a resource component, see the TransferMsg method.

```

1 HandleEvent()() | E : EventProperties |

in?event(E);

3

par

4

HandleEvent()()

5

and

6

TransferMsg()();

7

out!event(E)

8

rap.

9 TransferMsg()()

10

msg!transfer(MsgId, MessageSize);

msg?transferred(MsgTransferred

11

| MsgTransferred = MsgId).

12

```

Figure 3.16: POOSL specification of a functional communication component

## Chapter 4

# Modelling of Architecture characteristics

## 4.1 Introduction

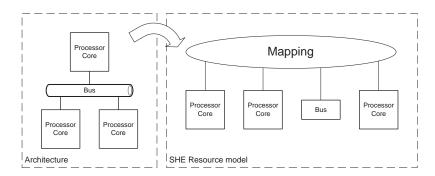

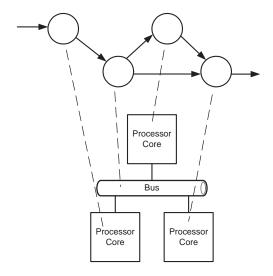

This chapter describes a method to model the hardware of a real-time embedded system. The hardware model encapsulates the hardware properties. As architectures are so diverse and complex, it is not possible to provide components that cover all possible system architectures. Therefore this chapter presents a set of basic components to model generic hardware structures, which can be used for specification of common (distributed) real-time embedded systems. In this section all physical architectural devices are specified as decoupled resource components as shown in figure 4.1. The interconnections of the architecture are implemented

Figure 4.1: Architecture modelled as decoupled SHE components

in the mapping section of this modelling approach. This technique provides a modular modelling approach which allows exploration of alternative architectures. Replacing architecture components is possible without changing the specification of other components. Figure 4.2 shows an example of specifying different architectures on a application model. In this example an architecture which consists of three processors and one shared bus is specified. Figure 4.2 shows an application graph which is mapped on resource components. The channels between the application model and resources model map each task on a resource component. Task 1,2 and 3 are computed on processor core A, B and C respectively. The communication between these task is performed on the bus resource component. A design exploration of a system which consist of two processors and one communication link can easily be established. By removing processor core B and

Figure 4.2: An example of a specification of an architecture which consist of three processor cores and one shared bus.

inserting a channel between task 1 and processor core C defines a real-time embedded system which consists of two processors and one shared bus. Figure 4.3 visualises the specification of an application performed on two processor cores and a shared bus.

Figure 4.3: An example of a specification of an architecture which consist of two processor cores and one shared bus.

This chapter is organised as follows:

- Section 4.2 describes several components to model the computational part of the hardware in a real-time embedded system.

- Section 4.3 describes how to model communication behaviour of the hardware.

## 4.2 Modelling of Computation

In this thesis, the processor component models the computation behaviour of the architecture. A simple processor component is given in figure 4.4. This computation component models task executions using a First Come First Served (FCFS) discipline. When a task is received (line 3) the component models a computation using the delay procedure (see line 4). When the computation terminates a message is returned to the application model (line 5).

To be able to model basic computation behaviour, it is useful to capture the commonly used scheduling policies. A commonly used scheduling policy is based on an off-line table-driven approach (time-slice scheduling), where the time line is divided into fixed-sized slices. Tasks are statically allocated to slots based on their

```

<< process >>

Computation

\overline{<<} instantiation parameters >>

MIPS : Real;

1 ComputeTask()()

<< instance variables >>

|Task : TaskElement, ComputationLoad:Real|

<< methods >>

3

execute?task(Task, ComputationLoad);

ComputeTask()()

delay ComputationLoad / MIPS;

5

executed!task(Task);

<< initial method call >>

ComputeTask()()

6

ComputeTask()()

<< messages >>

execute?task

execute!task

```

Figure 4.4: POOSL specification of a computation component without scheduler

rates (periods of execution) and execution requirements. A scheduling approach based on priorities is also commonly used. In this policy a priority is assigned (statically or dynamically) to each task and the execution order is generated online based on the current priority value. Two main scheduling algorithms based on priorities are Rate Monotonic (RM) and Earliest Deadline First (EDF). In the RM approach, tasks are assigned with fixed priorities according to their period. The task which needs to be executed at the highest rate receives the highest priority. Once the execution is started, the task can be preempted at any time by a task with a higher priority. With the EDF algorithm priorities are dynamically assigned to tasks, depending on their absolute deadline. EDF is harder to implement but may perform better results, see [22]. The next sections discuss the implementation of a processor model using an off-line table-driven, a RM and an EDF approach.

#### 4.2.1 Static Time Slicing Scheduling

Time slice schedulers assign a time slot to a task for computation. When the computation of the task is not able to be finished in time, the computation will be preempted and placed in a buffer. After this the scheduler activates the next process, see figure 4.5. This technique is comparable to Round Robin (RR) scheduling,

Figure 4.5: Task queue of a time line scheduling algorithm.

see [23]. Both scheduling policies assign a fixed computation time to each task. The RR scheduler is always (during execution) able to accept new tasks in the task queue (as First Come First Serve), where in static time slicing scheduling the order of process execution is fixed and assigned to a time slot by the engineer. The advantage of this approach is that the computation order is fixed when each process is dedicated to a time slot which is large enough to finish the computation. Assigning an execution (task) to multiple slots is allowed. When a process is not able to be finished in the assigned time slot(s), the process will be preempted which consumes time. On the other hand this scheduling approach is not suitable for execution of unknown processes, each task must be assigned to a slot before execution. Figure 4.6 shows the preemptive static time slicing scheduling algorithm specified in POOSL. The ContextSwitch and HandleTaskQueue methods

```

2

par

3

ContextSwitch()():

and

4

5

HandleTaskQueue(1)():

6

rap

7

ContextSwitch()()

8 | i : Integer | i := 1;

<< process >>

while i <= TaskQueue occupation do

9

Computation

10

activeTask := TaskQueue at(i);

<< instantiation parameters >>

11

delay SliceTime;

MIPS : Real;

12

i := i + 1

SliceTime :

Real;

13

od:

TaskQueue :

Dictionary;

14

ContextSwitch()().

<< instance variables

15 HandleTask(SliceId:

Integer)()

<< methods >>

16 | TaskId, SeveringTask: Integer,

ini()()

ComputationLoad : Real

17

ContextSwitch()()

18

SeveringTask := TaskQueue at(SliceId);

HandleTask()()

task?execute(TaskId | TaskId =

19

HandleTaskQueue()()

20

ServingTask);

<< initial method call >>

21

[activeTask = TaskId]

ini()()

22

delay ComputationLoad / MIPS;

<< messages >>

23

task!executed(TaskId):

task?execute

24

HandleTask(SliceId)().

task?executed

25 HandleTaskQueue(SliceId :

Integer)()

26

if TaskQueue occupation > SliceId then

27

par

28

HandleTask(SliceId)()

29

30

HandleTaskQueue(SliceId + 1)()

31

32

```

1 ini()()

Figure 4.6: POOSL specification of a preemptive computation resource based on the static time slicing scheduler

described in figure 4.6 at line 3 and 5 are executed in parallel. The tail-recursive ContextSwitch method changes the activeTask when a predefined time slice period has elapsed. The activeTask guard represents the identification of a task that is allowed to be executed. The method HandleTask is executed several times depending on the number of scheduled tasks. The most important issue in time slice scheduling is the size of a slice. When the time slice is set small, tasks with a short execution time are finished fast whereas tasks with large execution time are finished late. When task have a short deadline this must be avoided.

## 4.2.2 Priority Based Scheduling

Most priority based algorithms such as the Rate Monotonic (RM) approach are pre-emptive scheduling policies. This means that a context switch will take place when a task of a higher priority is received. In this method (see section 3.3.1) the priorities are assigned in the task at the application level. The priorities are assigned to tasks before execution and do not change over time. To comply to the RM approach tasks with shorter periods (higher request rates) will have higher priorities. Moreover, the following condition must be met; for every task i  $(i=1,2,3,\ldots), C_i < T_i$ , where  $C_i$  and  $T_i$  denotes the computation time and period of task i. To comply with RM scheduling each task must be independent and have a zero offset (for more details see [24]). In figure 4.7, the POOSL specification of a computation resource with priority based scheduling is presented, which also can be used for computation based RM scheduling. Note: For complying to the RM

```

1 HandleTask()()

task?execute(Task, ComputationLoad, Priority);

Computetask(Task, ComputationLoad, Priority)();

HandleTask()().

5 ComputeTask(ServingTask :

Integer, ServingComputationLoad :

ServingPriority : Integer)()

6

7

| ReqTask, ReqPriority : Integer, ReqComputationLoad : Real |

8

interrupt delay ServingComputationLoad / MIPS with

9

10

task?execute(ReqTask, ReqComputationLoad, ReqPriority |

11

ReqPriority > ServingPriority);

ComputeTask(ReqTask, ReqComputationLoad, ReqPriority)()

12

13

task!executed(ServingTask).

14

```

Figure 4.7: POOSL specification of computation with priority scheduling policy

scheduling discipline the priorities must be assigned with respect to their periods.

The initialisation method HandleTask is tail-recursive which becomes an endless running process. This procedure guarantees the handling of a computation request of a task. After receiving a task, which has a specific priority and computation load, the computeTask method is started. The computation is then preformed on line 8 with the delay statement. During the computation this process can be preempted with the interrupt statement. The computation will be preempted when a new task is received with higher priority (see line 10 and 11). When a task is preempted the ComputeTask method is started again (recursive). When a computation is able to be finished the ComputeTask method returns a task!executed message to the application level. When the ComputeTask is finished the tail-recursive procedure HandleTask is restarted.

#### 4.2.3 Earliest Deadline First Scheduling

The Earliest Deadline First (EDF) scheduling algorithm dynamically assigns priorities with respect to the absolute deadline of each task. As described in [22], EDF can results in less runtime overhead than RM, when context switches are taken into account. (It is commonly believed that EDF introduces a larger runtime overhead than RM, because in EDF absolute deadlines need to be updated from one task to the other. It is true that this needs extra computation time, but it reduces the costly context switches.) Replacing line 10 and 11 of figure 4.7 by the one given in figure 4.8, result in an EDF based computation model.

```

10 task?execute(ReqTask, ReqComputationLoad, ReqDeadline 11 | ReqDeadline > ServingDeadline);

```

Figure 4.8: This POOSL specification is needed in figure 4.7 to model a earliest deadline first scheduler.

## 4.3 Modelling of Communication Resources

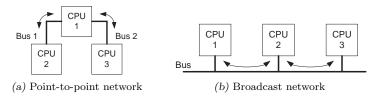

A communication resource is a facility to exchange data between processors (applications). Today many real-time embedded systems support more functionality by use of multiple processors. To exchange data these systems contain communication resources. [25] discusses several kinds of communication networks used in real-time embedded systems. As existing communication networks are so diverse and complex, it is not possible to provide components that cover all possible communication networks. In general, communication networks can be divided in point-to-point and broadcast networks as shown in figure 4.9. In simple point-

Figure 4.9: General communication networks

to-point communication network a task sends a message to another one by using a communication resource that has a direct connection between two processors. In common used point-to-point switched networks, where several switched are used, there is no direct connection. In this thesis, a simple example of a point-to-point resource used for a direct connection between two processors is specified. Figure 4.10 specifies a (simple) point-to-point communication component, which models message passing between tasks through the communication resource. This

```

<< \overline{	t process} >>

Point2PointCommunication

<< instantiation parameters >>

1 HandleMsg()()

Bandwidth : Integer;

2 | MessageId, MessageSize :

<< instance variables >>

msg?transfer(MessageId, MessageSize);

\overline{<<} methods >>

TransferingMsg(MessageSize)();

HandleMsg()()

5

msg!transferred(MessageId);

TransferingMsg()()

6

HandleMsg()().

<< initial method call >>

TransferingMsg(MessageSize :

HandleMsg()()

delay MessageSize / Bandwidth;

<< messages >>

msg?transfer

msg?transferred

```

Figure 4.10: POOSL specification of a direct point-to-point communication resource

point-to-point resource exchange data as First Come First Serve (FCFS). Method HandleMsg sequentially receives requests through the msg?transfer messages from the communication task model. When receiving a communication request, method TransferingMsg models a data exchange through the communication resource. The transfer time in this resource depends on the data(MessageSize) and bandwidth (see line 8).

Nowadays communication through a broadcasted network (shared medium)

is often used in embedded systems consisting of multiprocessors. A task sends a message through the network to another task running on a different processor. The presented example is able to model the basic behaviour of such networks. For example a central arbiter is neglected. As existing broadcast networks are so diverse and complex it is difficult to model each behaviour and therefore out of the scope of this thesis.

# Chapter 5

# Mapping

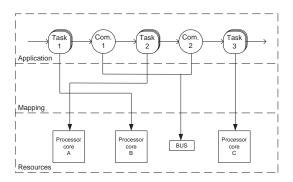

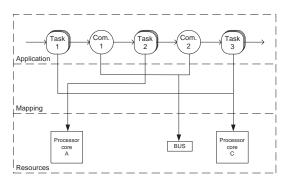

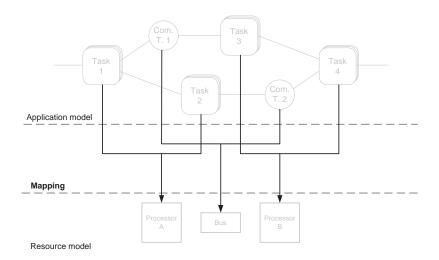

When the application and the architecture models have been defined as described in chapters 3 and 4, the design modelling can be continued using the Y-chart approach (fig 2.2). Mapping is the next section of the Y-chart. In this mapping phase, application components are dedicated to resource components. The task in the application graph will be executed on the resource components. In other words, the workload of the application is assigned to resource components in the architecture model. Figure 5.1 shows the mapping phase of the modelling methodology. This modelling method uses communication channels provided by

Figure 5.1: Mapping phase.

the POOSL language to map application components to resource components. Figure 5.2 shows an application model mapped on an architecture model specified using the earlier described modelling approach. The figure shows three sections of the Y-chart, namely the application, mapping and architecture(resource models). Creating a mapping channel in SHEsim is done by creating a message channel between the task and the resource components. In this figure (software) task 1 to task 4 and communication task 1 and 2 are defined in the application model. (Software) Task 1 and 2 are mapped on processor A (a resource component). Task 1 will be executed, with respect to the scheduling policy, on processor A when an event has triggered the application model. When processor A has finished the execution of task 1, it sends a message back to task 1 (consuming no time).

Figure 5.2: Mapping of application and architecture models where the communication channels defines the hardware structure of the system.

When task 1 receives this message, it triggers task 2 and communication task 1. Task 2 will then be executed on processor A and communication task 1 on the bus resource. This process will continue till task 4 is executed on processor B. The outgoing event at task 4 can be used for analysis purposes. Figure 5.3 shows a possible sequence diagram of the communication which takes place between the application and the resource components. This sequence diagram visualises

Figure 5.3: Sequence diagram of communication for execution demand in the mapping phase.

the communication between a task in the application level and a processor in the resource level. A task component sends the message task!execute to a resource component. The resource component receives this message with a task identification, computation load and a priority. This exchange of data consumes no time. The resource component will execute (with respect to a scheduling policy) the computation load with the delay statement. This execution will consume time. When the execution is finished the resource component sends a task!executed with the task identification back. The application will only accept messages where the identification is identical of the original. This must be

checked because multiple tasks can be mapped on one resource.

A possible extension of this work is to define a dynamic mapping approach. This is possible because this model is specified modular. The dynamic mapping approach must use the same message protocol used between the application components and resource components. This extension is out of the scope of this thesis and therefore proposed as future work.

# Chapter 6

# A case study: Distributed In-car radio navigation system

#### 6.1 Introduction

This chapter describes the application of the modelling approach proposed though a case study. This case study, an in-car distributed radio navigation system, is presented in [26]. This is a realistic and well defined system and therefore interesting for performance analysis. In [26] the system is evaluated using Modular Performance Analysis (MPA). MPA is an alternative, analytical performance analysis approach based on the Real-Time Calculus developed at ETH Zurich.

The first section gives a description of the case study. Next the POOSL implementation using the modelling approach defined of chapter 3 to chapter 5. Section 6.3 presents the performance results obtained from the POOSL model. The MPA analysis of the case study is discussed in section 6.4 and followed with a comparison of the POOSL and MPA results (section 6.5). The final section discusses average performance analysis.

### 6.2 Distributed In-Car Radio Navigation System

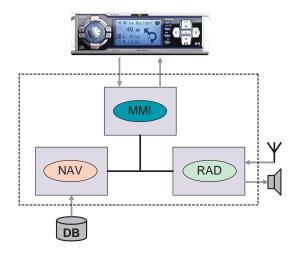

The case study presented in [26] is inspired by a system architecture definition for a distributed in-car navigation system. An overview of the system is presented in figure 6.1. It is composed of three main clusters of functionality:

- The Man-Machine Interface (MMI) which takes care of all interaction with the user, such as handling key inputs and graphical display output.

- The navigation functionality (NAV) which is responsible for destination entry, route planning and turn-by-turn route guidance giving the driver both audible and visual advices. The navigation functionality relies on the availability of a map database, typically stored on a CD or DVD, and positioning information, e.g. speed and Global Positioning System (GPS). The latter is not shown here.

- The radio functionality (RAD) which is responsible for basic tuner and volume control as well as handling of traffic information services such as Radio Data System (RDS) / Traffic Message Channel (TMC). RDS TMC is broadcast along with the audio signal of radio channel.

Figure 6.1: High-level of a distributed radio navigation system

The key question that is investigated in [26] is how to distribute the functionality over the available resources, such that we meet our global timing requirements. The functionality is specified with Use-Cases and their associated sequence diagrams. The three selected distinctive scenarios that are used for performance analysis are:

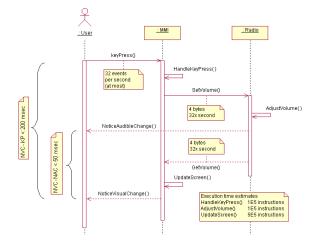

1. "Change Volume" - The user turns the rotary button and expects instantaneous audible feedback from the system. Furthermore, the visual feedback (volume setting on the screen) should be timely and synchronised with the audible feedback. This seemingly trivial Use-Case is actually quite complex because many components are affected. Changing volume might involve commanding a digital signal processor (DSP) and an amplifier in such a way that the quality of the audio signal is maintained while changing the volume. This scenario is shown in detail in figure 6.2. Note that three operations are identified, HandleKeyPress, AdjustVolume and UpdateScreen. Execution times, event rates and message sizes are estimated and annotated in the Sequence Diagram together with the main timing requirements applicable to this scenario.

Figure 6.2: Annotated Sequence Diagram for "Change Volume"

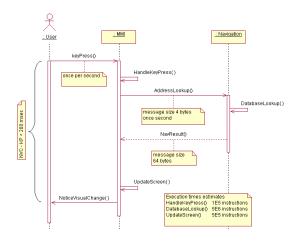

2. "Address Look-up" - The destination entry is supported by a smart "type-writer" style interface. By turning a knob the user can move from letter to letter. The map database is searched for each letter that is selected and only those letters in the on-screen alphabet are enabled that are potential next letters in the list. This scenario is shown in detail in figure 6.3. Note that the *DatabaseLookup* operation is expensive compared to the other operations and that the size of the output value the operations and that the size of the output value of operation is 16 times larger than the input message.

Figure 6.3: Annotated Sequence Diagram for "Address Look-up"

3. "TMC Message Handling" - Digital traffic information is very important for in-car radio navigation systems. It enables features such as automatic replanning of the planned route in case a traffic jam occurs ahead. It is also increasingly important to enhance road safety by warning the driver, for example when a ghost driver is spotted on the planned route. RDS RMC is such a digital traffic information service. TMC messages are broadcast by radio stations together with stereo audio sound. RDS TMC message types are transmitted. The map database is accessed to translate these identifiers and to construct human readable text. The TMC message handling scenario is shown in figure 6.4.

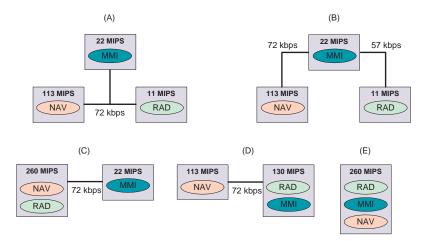

The above presented scenarios can occur in parallel, which means that the system receives TMC messages while a user is pressing the rotary knob. The architectures shown in figure 6.1 suggest to assign the three clusters of functionality each to its own processing unit. Figure 6.5 propose more potential architectures that might be applicable. Those architectures are specified from datasheets of several commercially available automotive CPUs.

Figure 6.4: Annotated Sequence Diagram for "TMC Message Handling"

Figure 6.5: Alternative system architecture to explore

#### 6.3 POOSL Model